Part one of this blog discussed basic needs of a Limited Power Source (LPS) and provided a brief overview of standards that govern LPS circuits.

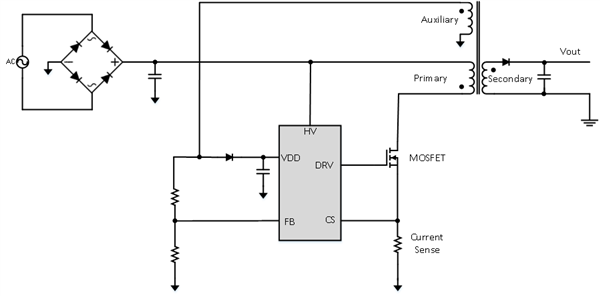

To address the needs of protection and limiting, conventional power supplies as illustrated in Figure 1 rely on multiple feedback loops based on two or more optocouplers. These optocouplers transmit the load voltage, load current and open-fault information to the main controller – typically a flyback controller for wattages up to 150W. In addition, the current-sensing circuitry has external current-sense resistors, precision operational amplifiers for amplification and setting the constant current-constant voltage (CC-CV), and constant power feedback loops. Overall, discrete circuits have high component counts, use up valuable real estate on the board and add cost to the system.

Figure 1: Typical block diagram showing the conventional architecture of a 100W industrial power supply

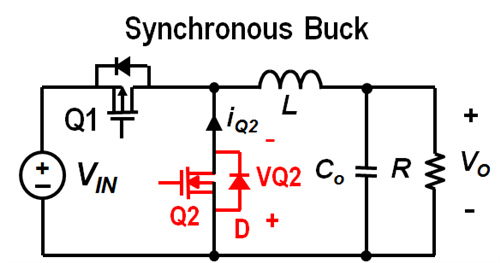

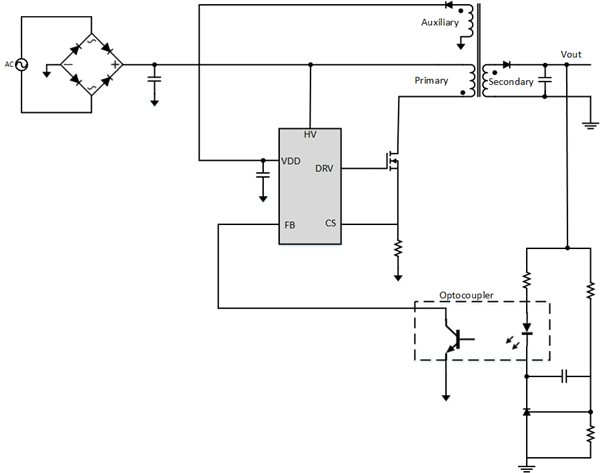

Figure 2 shows a proposed design architecture with reduced feedback loops. The architecture uses the UCC28740, a CC-CV flyback controller with optocoupled feedback for voltage and primary-side regulation (PSR) for constant current. The high level of integration of the controls in the UCC28740 controller aids in low component count design and reduced cost.

Figure 2: Proposed design architecture with reduced feedback loops

The two key benefits of this proposed architecture are:

- Precise current and power limit, just with primary-side sensing. In the conventional approach shown in Figure 1,The output load current is sensed through discrete operational amplifier circuits and transmitted to main controller through opto-coupler. In some cases an additional opto-coupler is used for feedback redundancy. the output load current is directly sensed and the information is fed back to the flyback controller through a separate optocoupler circuit. The proposed architecture, on the other hand, uses cost-effective and reliable primary-side current sensing. A high degree of precision in the output-current limit is made possible by precision PSR current-sense techniques embedded into the UCC28740. The current limit causes the voltage foldback and ensures tight power limiting.

- Cost-effective open-loop protection and feedback redundancy. The conventional approach shown in Figure 1 uses two feedback loops, both of which are based on optocouplers. The identical nature of these optocouplers and their associated circuitry bring in an additional risk of failure; each of the optocouplers can fail simultaneously under similar stress conditions, which can be detrimental.

The proposed architecture uses a single optocoupler feedback precision-output voltage control. A PSR circuit provides a redundant voltage-control loop. PSR activates during open-loop conditions such as failure in the optocoupler feedback network. Thus, output voltage is limited and regulated to the value set by as the primary-side feedback components.

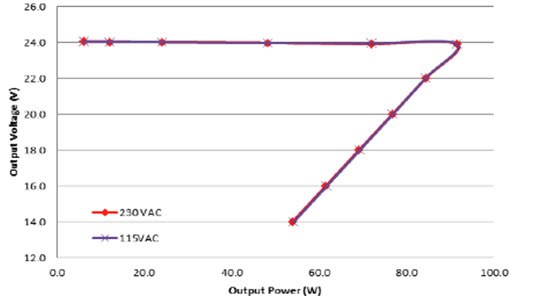

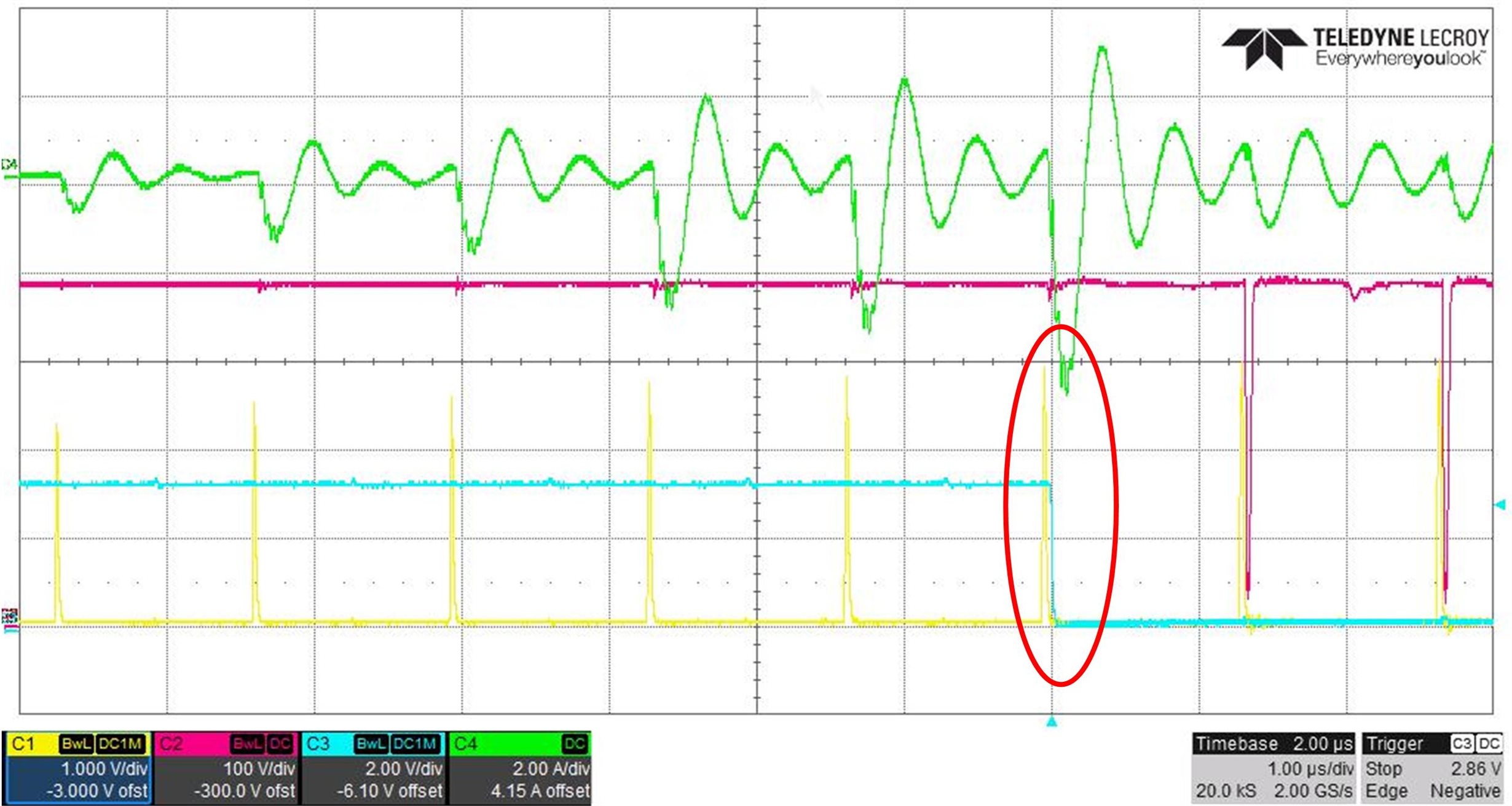

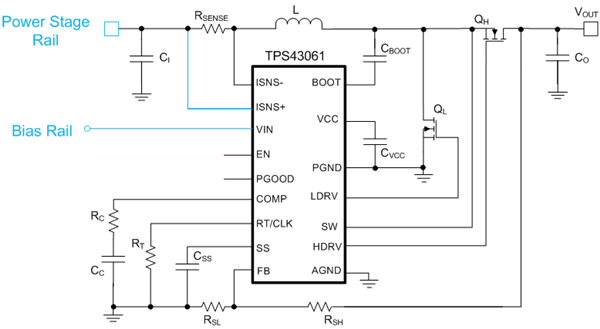

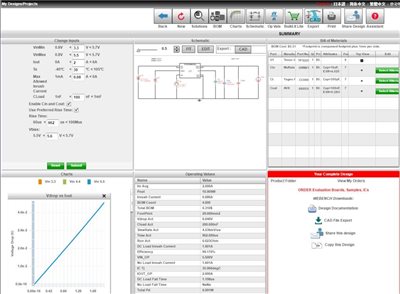

The 60W, 24V High Efficiency Industrial Power Supply with Precision Voltage, Current and Power Limit highlights the performance results of precision current and voltage limiting. Figures 3 and 4 show the results of the reference design board for precision current regulation and power foldback.

Figure 3: Precision CC-CV operation

Figure 4: Precision power foldback characteristics

Additional resources

Explore these industrial power-supply reference designs:

- 100W, 24V High Efficiency High PF Industrial Power Supply with Precision Current and Power Limit.

- 60W, 24V High Efficiency Industrial Power Supply with Precision Voltage, Current and Power Limit.

References

IEC60950-1 Information Technology Equipment - Safety - Part 1: General Requirements

NFPA 70: National Electrical Code (NEC) standard