Remember the blog with an interesting analogy between power factor correction (PFC) and beer earlier this year? I think it is brilliant! In that case, the beer in a glass represented the “real power” that an electronic device actually requires, the foam at the top represented “reactive power,” and the entire glass of beer plus the foam represented the “apparent power.” Today, I’m taking on the challenge of proposing a related analogy to explain the role that a gate driver plays in PFC designs.

Let’s briefly talk about the different types of PFC circuits first. In general, PFC circuits are either passive or active. To create passive PFC circuits, you add passive components like capacitors and inductors to increase the current conduction angle and smooth down the pulse, which helps reduce the current’s harmonic distortion. This approach is simple and reliable, but the size and cost of the passive components becomes a big problem when the power level is high. A passive PFC design can also only achieve a power factor (PF) up to 0.9 and is affected by frequency, load change and input voltage.

Active PFC uses a DC/DC circuit, which contains MOSFETs, insulated-gate bipolar transistors (IGBTs) or other active components to force the current to follow the voltage in both shape and phase. Compared to passive PFC, active PFC can achieve higher PF and does not have strict requirements on the input voltage. Drawbacks of active PFC include comparatively complex circuitry; also, the efficiency can be affected by the losses of active components.

There are different topologies to realize active PFC circuits, such as boost PFC (also known as traditional PFC), dual boost bridgeless PFC and totem-pole bridgeless PFC. Each topology contains a different number of active components and has its own pros and cons. When designing a PFC, you should consider the efficiency and power ratings of each topology and then determine which type of controller to use. However, one part many designers ignore is the gate driver that’s connected to the controller to switch the FETs. Gate drivers seem too common to bother with, but they play an important role in the performance of the system.

A gate driver is essentially an amplifier that boosts the logic signal to a high current and high-voltage signal that turns the MOSFET or IGBT on and off quickly, with the least switching loss. To make an analogy also related to beer, power-switch MOSFETs or IGBTs are like the beer-tap handle, the gate drive is like the muscles in the bartender’s hand and the controller is the brain. The skills of the bartender and the quality of the tap handle can both impact how much beer you actually get in a glass.

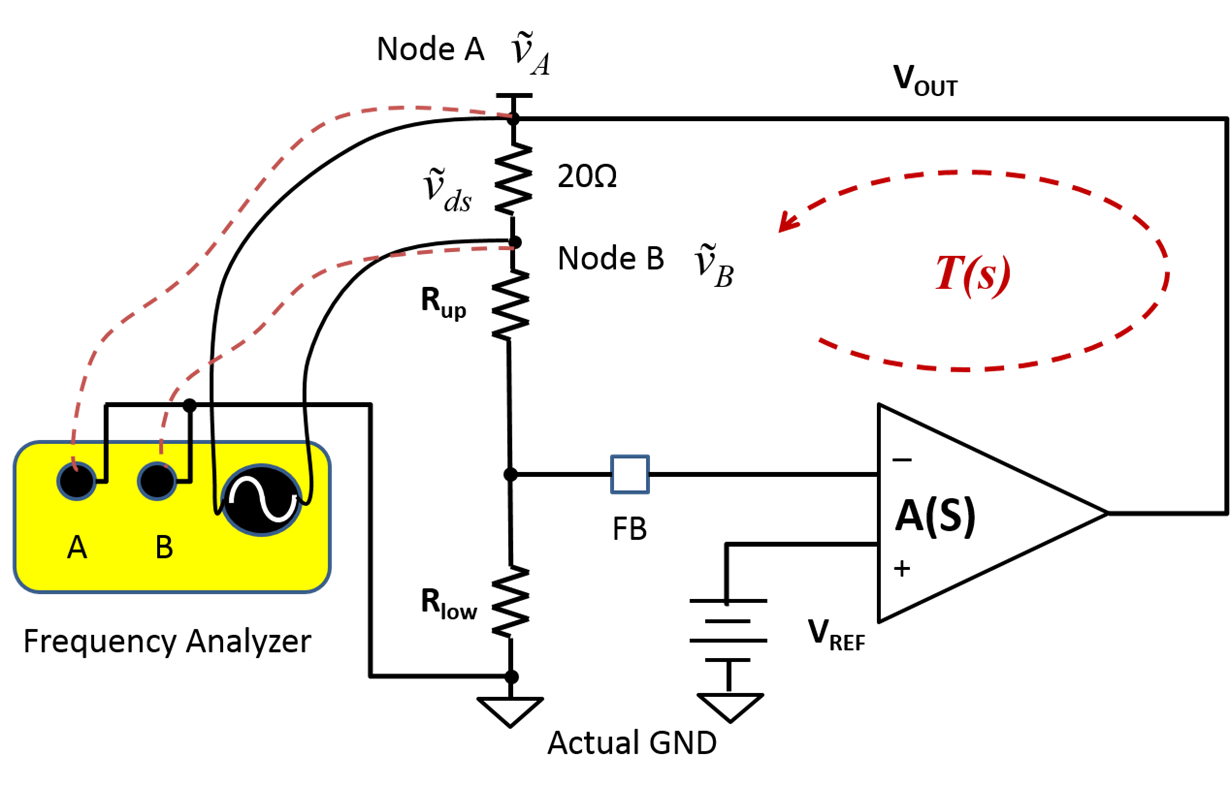

In PFC circuits, gate drivers switch the transistors in the boost stage to regulate the current and force it to be in phase with the sine-wave voltage. So how does the gate driver affect PFC circuit performance? Several parameters and features play a vital role:

- Drive current. Although not every application demands a strong current drive (given the potential electromagnetic interference (EMI) issues caused by a big transient), the higher-power applications will require a stronger current drive to drive multiple FETs at the same time. Therefore, a high drive current provides flexibility in a wide range of power applications.

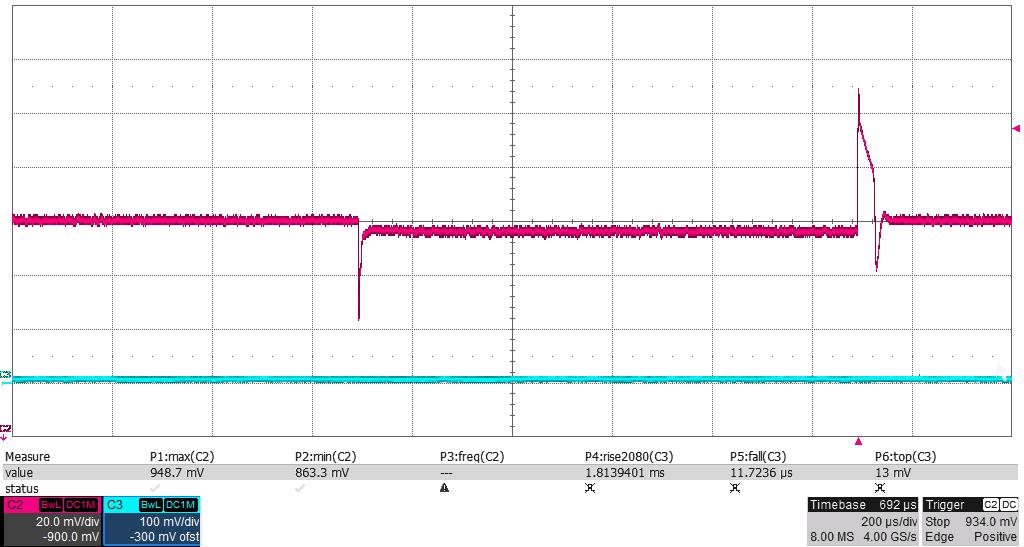

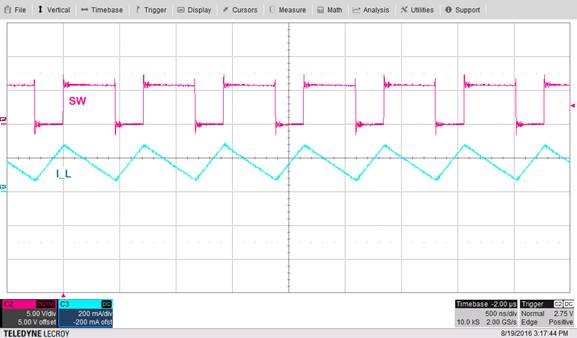

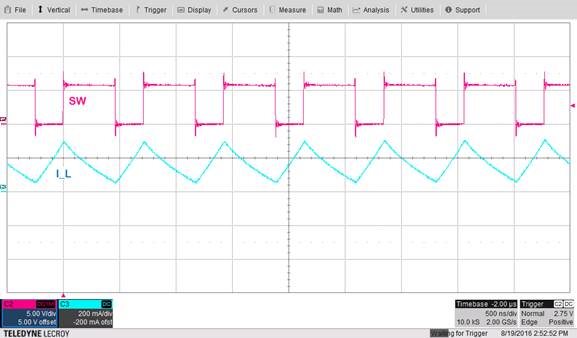

- Switching characteristics. These include propagation delays, delay matching, and signal rise and fall time. The switching timing will greatly impact the speed of the power switch and will make the control more predictable and accurate. Short delay matching also reduces the risk of shoot-through and makes the challenge of designing easier.

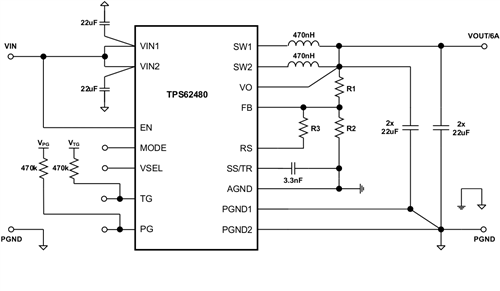

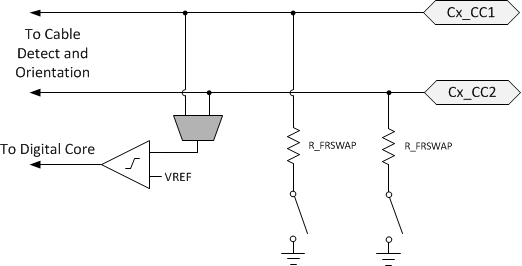

- Interlock feature. Shoot-through protection, also known as an interlock feature, is critical in some applications using half-bridge or full-bridge circuits. In totem-pole PFCs, two power switches (one high-side FET and one low-side FET) turn on and off alternatively. If both switches turn on at the same time, the current will flow through both FETs and possibly damage the system. The interlock feature can prevent this shoot-through from happening, resulting in both FETs being off for a short amount of time before one of them turns on. As described in Texas Instruments’ “GaN FET-Based CCM Totem-Pole Bridgeless PFC” Power Supply Design Seminar paper, the design uses two silicon MOSFETs and two gallium nitride (GaN) high-electron-mobility transistors (HEMTs) to minimize conduction loss. Two drivers are needed: one half-bridge driver to drive the regular silicon MOSFETs and one half-bridge driver to drive the GaN transistors. TI’s 600V LMG3410 GaN power stage integrates a bridge driver and a GaN transistor into one package, which further decreases power loss and improves EMI. To drive the silicon FETs, a bridge driver with the interlock feature improves design reliability.

PFC will be used more and more in various applications as regulations make higher efficiency mandatory in more countries. Pick your topologies and components wisely so that your PFC can work efficiently and fit your needs. And don’t forget gate drivers – the muscle.

Gate driver’s importance should be clear now, but the brain plays an even more important role in PFC designs. Texas Instruments offers a broad range of PFC controller solutions, including analog and digital controllers for both single and multiphase interleave PFCs.

Explore all the PFC controllers and high voltage gate drivers from Texas Instruments.

Additional resources

- Check out TI’s low-side and bridge gate drivers to find the most suitable solution for your PFC design.

- Read the blog post, “Are you ready for totem-pole PFC?”

(1)

(1)