Universal Serial Bus or “USB” has been around for a long time; at the very beginning, USB had exclusive primary and secondary hosts. The primary data transmission was mainly from the PC and the secondary transmission was to mobile phones, mice or keyboards. With the development of consumer electronics, however, the demand for data transmission from the smartphone to the USB drive, tablets to smartphones and cameras to the printer has increased.

USB On-the-Go (OTG) is a specification that enables devices to act as either a primary or secondary host. USB OTG is widely adopted in PCs, smartphones, EPOS (Electronic point-of-sale) and power banks. The roles of primary and secondary hosts can change according to the protocol. Data can be stored in a USB drive from a smartphone or camera and the smartphone can also act as the secondary host when connecting to a PC as a primary, for example. Digital camera photos can directly upload to the printer and no longer have to be transferred by a PC. Data transfers between the “secondary” and “secondary” hosts. It’s really amazing and useful in our daily life. Figure 1 shows a USB OTG disk and some USB OTG cables in the market.

Figure 1: USB OTG drive (left) and USB cables (right)

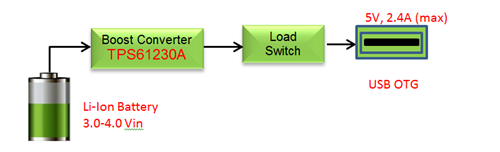

The OTG function is very popular in portable devices, most of which are powered from lithium-ion (Li-ion) batteries (2.7V to 4V). A boost converter is needed for USB OTG power supplies (typically 5V).

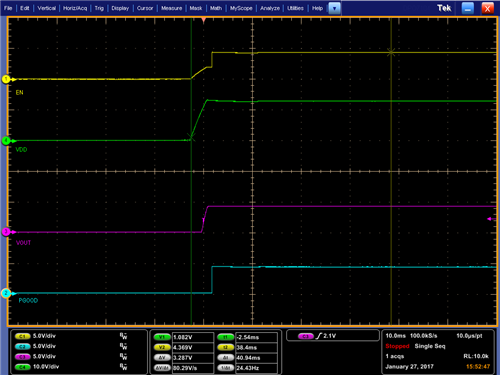

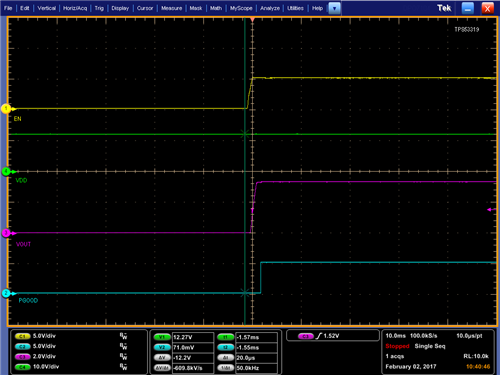

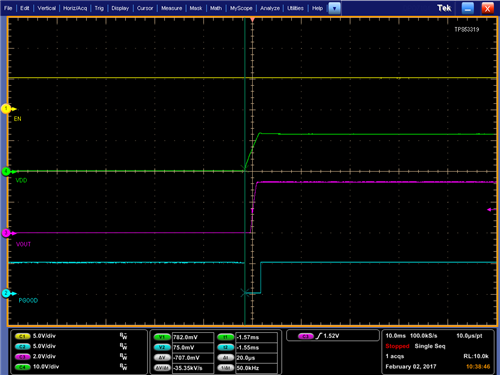

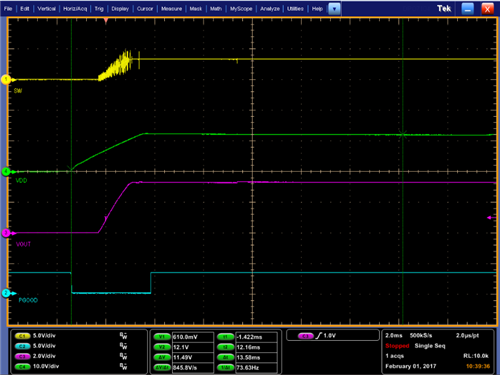

With data speeds increasing, the USB Implementers Forum has updated the power specification several times, announcing the newest USB Power Delivery (PD) specification for USB OTG devices in 2016. In this USB PD specification, the maximum current at 5V is 3A.TI’s high efficiency step-up converter, the TPS61230A, can cover most applications for this specification. For most portable devices, package size and thermal performance are critical because of the limited space inside smartphones. The TPS61230A achieves a good balance between size and performance (efficiency, thermal), and meets the maximum 5V/2.4A power demand of USB PD from the Li-ion battery, as shown in Figure 2.

Figure 2: Block diagram for USB OTG Vbus power supply

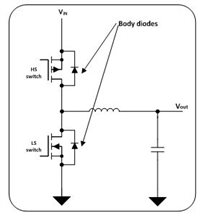

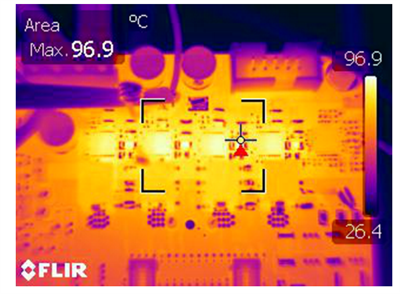

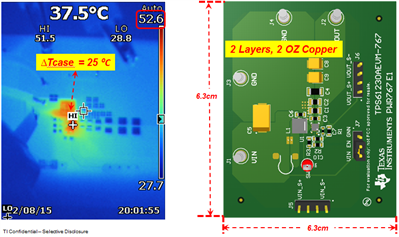

The TPS61230A is based on a valley current-limit mode-control scheme with a 4.8A minimum switch current limit. The device integrates two low RDS(on) FETs (18mΩ/high speed, 21mΩ/low speed) which results in higher efficiency as well as good thermal performance. Only 25°C temperature rise will be achieved with VIN=3.6V, VOUT=5.0V, IOUT=2.0A under room temperature condition as shown in figure3.

Figure 3: Thermal Performance and EVM

The TPS61230A frequency can be as high as 1.15MHz to enable small-sized inductors and capacitors. The TPS61230A is compact; the QFN(Quad-flat no-leads) 2mm-by-2mm package has only seven pins out. The enhanced power bus underneath the package facilitates thermal dissipation (the thermal resistance is 56°C/W with vias underneath the power bus). The TPS61230A is very easy to design in power systems, while the seven pins out make printed circuit board (PCB) layout very easy.

Figure 4 shows the efficiency curves with different input voltages. The TPS61230A has an excellent output capacity of 3A at VOUT = 5V and VIN = 3.6V; efficiency can be as high as 94%.

Figure 4: Test condition: VOUT = 5V, L = 1µH (XFL4020-102MEB)

In summary, thanks to the low on-resistance of both high-side and low-side MOSFET, TPS61230A can make your design more compact, much cooler but even more powerful.