Let’s talk power – the kind you can relate to. Your phone charger, tablet charger and notebook computer adapter. Take a good hard look at them, because they will never be the same.

Key forces are leading to a seismic shift in the high-volume, low-cost world of consumer electronics that we love to hate.

How would you like to have one universal charger that could work with all of your mobile electronics – your portable Bluetooth® speaker, DLP® movie projector or anything else that you eventually need to plug in to charge?

What would it mean to you to be in another country and see a charging port that you recognize built into the wall at a hotel, airport or restaurant?

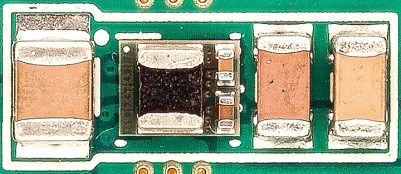

And what if that charger, which once gave you a workout just to carry, could now fit in the palm of your hand – and charged your phone from 0 to 80% in five minutes or your computer in 10 minutes?

It sounds good to me, but how is this happening? Let’s take a look.

- · Mobile charger power for smart phones and tablets is increasing. Battery-charging architectures are changing. Whereas once a buck converter chopped down the 12V adapter supply voltage to something more manageable by a single cell, now the adapter charges the battery at exactly the right voltage and current that the battery demands in real time in its charging cycle. What once was 5, 10 or 15W is now 27, 36 and 45W as processing power and batteries increase in capability and capacity (but our patience for charging continues to diminish).

- Notebook/laptop powers are decreasing.Yes, there are still 65W hogs out there, but we now have chromebooks, ultrabooks and everything in between, driving a mid range of power from 27W-45W. This will fill the gap between tablets and classic notebook adapters in terms of power required, blurring the boundary between a phone charger and a high-power adapter.

- · The arrival of USB Type-C™ port and USB Power Delivery (PD). We may really have one charger to rule them all. From the standard universal, bidirectional USB Type-C connector to the USB PD protocol that powers anything from 5W to 100W (which is basically every electronic product you can imagine), we now have a smart and capable power supply. Our penchant to save the world also plays a small role, as reducing electronics waste begins to factor into the consumer choice equation.

- · Evolving travel adapters. I hate to admit it, but between my wife and I, we have two smartphones, three tablets and three laptops. At any given time I’m charging multiple devices at once. When we travel it’s no different. We are starting to see travel adapters with two and three ports instead of just one. As expected, that means more power needed, but not more space.

- · When is the government going to raise energy efficiency standards again? Last year we saw the latest EPS standard in the DoE’s Level VI version, requiring minimum performance in terms of four-point average efficiency as well as standby power. As usual, semiconductor vendors partnered early with power-supply manufacturers to meet the requirement, but what happens when the DoE raises the bar again? Will industry innovation outpace the next targets in time?

- · Wall sockets are changing.We’re starting to see USB outlets rather than AC outlets in homes, airports, hotels, restaurants and other venues. USB Type A and USB Type-C are now directly available in homes and buildings, saving you the trouble of dragging out your hulking AC/DC power brick by burying it in the wall or table. Could this be the end of AC wall outlets? Could we move exclusively to wireless and USB direct power? That sounds safer to me, and more convenient.

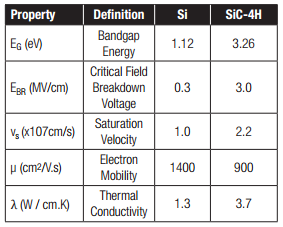

- · Super junction silicon power metal-oxide semiconductor field-effect transistors (MOSFETs) are getting better, and gallium nitride (GaN) FETs are getting cheaper and more integrated. Instead of being elusive, fancy concepts for the distant future, these advanced technologies are becoming tools for power-supply designers in low-power AC/DC applications.

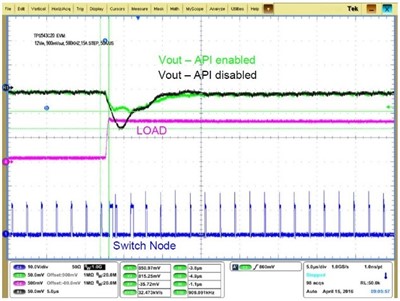

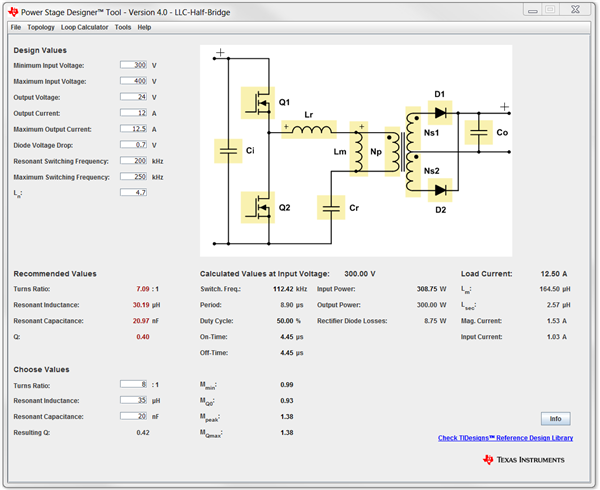

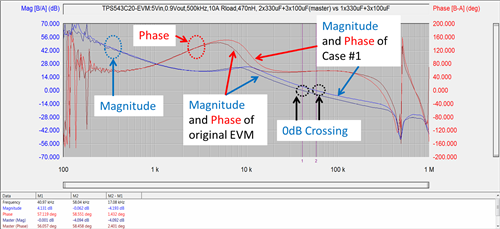

- · The standard single-switch flyback topology has been fully optimized. OK, I said it. I know you’ve all been thinking it. An amazing workhorse in the power electronics world, controllers for the flyback topology have seen added features over time including variable frequency, valley switching, MOSFET integration and multimode continuous conduction-plus-quasi-resonant operation to increase efficiency, all while driving down solution costs and continuing to meet stricter Department of Energy (DoE) and Code of Conduct (CoC) external power supply (EPS) standards. This arena now practically begs for a bold advancement beyond the incremental gains of the last decade.

AC/DC mobile chargers and adapters have largely used the same technology for the last decade and the market hasn’t demanded drastic change from this capability. Being involved in this industry, it’s exciting to see that this could all change very soon.

Maximize your power conversion with TI's comprehensive portfolio of isolated converters and controllers.