Almost all modern-day industrial systems involve an AC/DC power supply, which takes energy from the AC grid and delivers it to electrical equipment as a well-regulated DC voltage. With power consumption increasing around the globe, the associated energy loss in the AC/DC power-conversion process becomes a significant component of the overall energy cost equation for power-supply designers, especially those working on power-hungry telecom and server applications.

Gallium nitride (GaN) can help increase energy efficiency and reduce losses in an AC/DC power supply, which in turn helps lower the cost of ownership of the end application. For example, by enabling an efficiency gain as little as 0.8%, GaN-based totem-pole power factor correction (PFC) can help a 100-MW data center save as much as $7 million in energy costs over 10 years.

Choosing the right PFC stage topology

Government regulations worldwide mandate the use of a PFC stage in the AC/DC supply in order to facilitate a clean power draw from the grid. A PFC shapes the AC input current to follow the same shape as the AC input voltage, which maximizes the real power drawn from the grid, making the electrical equipment act like a pure resistor with zero reactive power.

As shown in Figure 1, traditional PFC topologies include the boost PFC (with a full-bridge rectifier after the AC line) and dual-boost PFC. The classical boost PFC is a common topology that contains a front-end bridge rectifier that has very high conduction losses. The dual-boost PFC reduces conduction losses since it does not have a front-end bridge rectifier, but it does need an additional inductor, and thus suffers in terms of cost and power density.

Figure 1: PFC topologies: dual-boost PFC (b); boost PFC

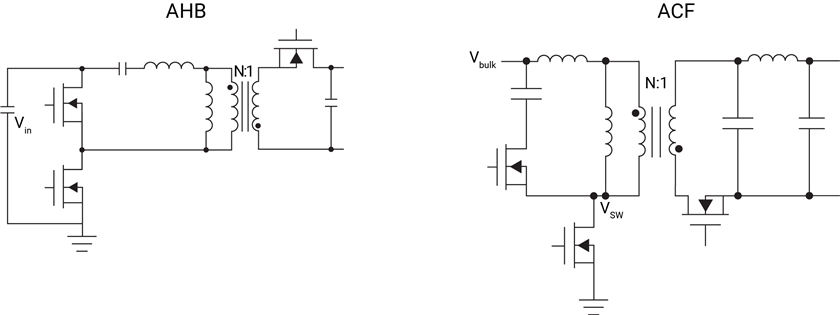

Other topologies that may increase efficiency include AC-switch bridgeless PFC, active-bridge PFC and bridgeless totem-pole PFC, shown in Figure 2. The AC switch topology uses two high-frequency field-effect transistors (FETs) conducting during the on-state and one silicon carbide (SiC) diode, plus a silicon diode, conducting during the off-state. Active-bridge PFC simply replaces the diode bridge rectifier connected to the AC line with four low-frequency FETs, which require additional control and driver circuitry. Active-bridge PFC uses three FETs conducting during the on-state and two low-frequency FETs, plus one SiC diode conducting during the off-state.

In comparison, totem-pole PFC has just one high-frequency FET plus one low-frequency silicon FET conducting during both the on-state and off-state, offering the lowest power losses among the three topologies. In addition, totem-pole PFC requires the fewest number of power semiconductor components to implement, which makes it an attractive topology when considering overall component count, efficiency and system cost.

Figure 2: Various PFC switch topologies that increase efficiency

Benefits of GaN in a totem-pole PFC

Traditional silicon metal-oxide semiconductor FETs (MOSFETs) are not a good fit for totem-pole PFC, as MOSFETs have a body diode with a very high reverse-recovery charge, causing high power losses and the risk of shoot-through damage. SiC power MOSFETs represent a marginal improvement over silicon, with lower reverse recovery from the inherent body diode.

Alternately, GaN offers zero reverse-recovery losses, with the lowest overall switching energy loss among the three technologies – over 50% lower versus comparable SiC MOSFETs. This is primarily because of the higher switching-speed capability of GaN (100 V/ns or higher), lower parasitic output capacitance and zero reverse recovery. The lack of a body diode in GaN FETs eliminates the risk of shoot-through entirely.

TI recently worked with Vertiv on a design that helped achieve a 98% peak efficiency in their 3.5-kW rectifier, achieving a 1.7% efficiency gain compared to the 96.3% peak efficiency of their previous-generation silicon 3.5-kW rectifier. To extrapolate this efficiency benefit to a real example, the use of GaN-based totem-pole PFC enables a 100-MW data center to save as much as $14.9 million in energy costs over 10 years, along with the added benefit of reduced carbon dioxide emissions.

The lack of reverse-recovery losses and reduced output capacitance and overlap losses in TI GaN enabled Delta Electronics to reach up to 99.2% peak efficiency in energy-efficient server power supplies for data centers. The integrated gate driver inside the TI GaN FET allows the FET to reach switching speeds up to 150 V/ns, lowering overall losses at high switching frequencies and enabling Delta to achieve an 80% improvement in power density, while increasing efficiency by 1%.

The benefits offered by GaN technology in totem-pole PFC designs are undisputable. As more power-supply unit designers switch to GaN, and as GaN manufacturers release innovative products, telecom and server power designers can expect continuous improvements in power density and energy efficiency.

Additional resources

- Check out these TI reference designs:

- Read the Analog Design Journal article, “Improve Power Density with a Baby Boost Converter in a PFC Circuit.”

- Learn more about TI and Delta’s collaboration.